چگونه طراحی برد مدار چاپی FPGA را برای سیستم های نهفته شروع کنیم؟

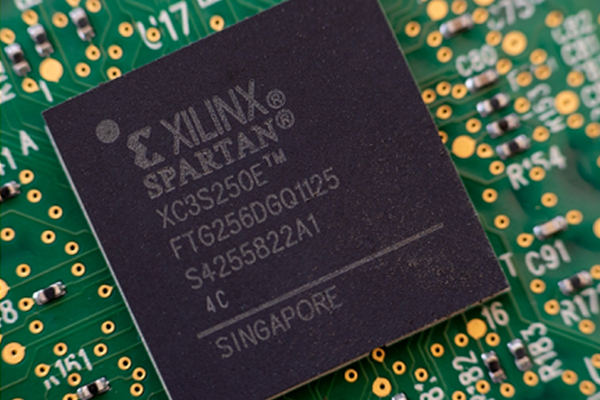

FPGA های چهارگانه یا پکیج BGA میتواند نقشهکشی آنها دشوار باشد، به خصوص زمانی که تعداد بالایی ورودی/خروجی داریم که اغلب در این مؤلفهها پیادهسازی میشوند. FPGA ها بدلیل داشتن قابلیت پیکربندی مجدد، مزایای زیادی دارند، اما برای چیدمان و مسیریابی میتواند به تلاش زیادی نیاز داشته باشند. اگر هرگز با یک FPGA در طراحی PCB خود کار نکرده اید، در این مقاله دستورالعمل هایی داریم که می تواند به شما در شروع طراحی برد مدار چاپی FPGA کمک کند.

طراحی برد مدار چاپی FPGA عمدتاً دشوار است زیرا به نقشه کشی قابل توجهی نیاز دارد که باید با طرح کلی سیستم مطابقت داشته باشد. طراحی سیستم FPGA می تواند تعیین کند که برخی از قطعات باید کجا قرار بگیرند وچگونه مسیریابی شوند و بالعکس. اگر قبلاً چیدمان سیستم خود را طبق پلان انجام داده اید ، احتمالاً زمان کمتری برای ساخت اپلیکشن خود و اجرای موفقیت آمیز آن بر روی یک FPGA صرف کنید.

برای شروع، ما به استک آپ (stackup) و کانال مسیریابی در FPGA خود خواهیم پرداخت، زیرا این نقاط انتخابهای زیادی را در طرح PCB برای ما ایجاد میکنند.

استک آپ و مسیریابی برای طراحی برد مدار چاپی FPGA

برای شروع کار با FPGA، توجه به این نکته مهم است که FPGA های پیشرفته امروزی با تعداد زیادی ورودی/خروجی در بسته های BGA عرضه می شوند. FPGA در QFP ها نیز هستند، اما پیشرفته ترین کامپوننت ها در بسته های BGA موجودند. دلیل این امر ساده است: اگر یک FPGA در پکیج BGA قرار داده شود می توان تعداد بیشتری ورودی / خروجی در یک بسته BGA قرار داده و اندازه کامپوننت راکاهش داد

بنابراین برای شروع، مطمئن شوید که استک آپ را برای طراحی برد مدار چاپی FPGA خود به گونه ای انجام داده اید که الزامات ساده زیر را برآورده می کند:

- ترکیب تغذیه و لایه های سیگنال با لایههای گراند در PCB stackup

- استفاده از روش استاندارد در BGAها برای تعیین تعداد لایه های سیگنال لازم برای مسیریابی (لایه های سیگنال = # تعداد سطرهای سیگنال/۴)

- برای ورودی/خروجی های پرسرعت، مطمئن شوید که لایه بیرونی را به اندازه کافی نازک کرده اید تا نیاز به حذف Neck-Down نباشد.

- استفاده از سطوح گراند و یا پر کردن گراند برای پشتیبانی از مسیریابی با سرعت بالا با کنترل امپدانس،

دستورالعملهایی که در اینجا برای طراحی برد مدار چاپی FPGA بیان شدهاند می توان برروی هر BGA ای پیاده کرد، اما در FPGA بسیار مهم هستند. به همین دلیل اغلب مواقع در FPGA استفاده می شوند برخلاف کامپوننت های کندتری مانند MCU/MPU به چندین رابط پرسرعت اجازه دسترسی می دهد.

حتی در BGAهای زیر میلیمتری نیازی به اجرای شیوههای طراحی HDI نیست، اما همچنان باید یک stackup را پیادهسازی کنید که نوع مسیریابی مورد نیاز برای اطمینان از یکپارچگی سیگنال، توان و EMC را ایجاد میکند.

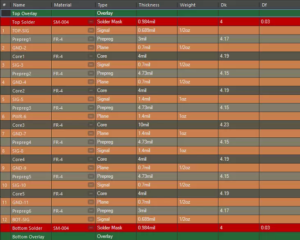

مثال استک آپ

استک آپ نشان داده شده در زیر، کانال مسیریابی چندگانه را در لایه های مختلف ارائه می دهد. اگر بیش از دو ردیف/ستون، I/O در FPGA وجود داشته باشد، باید چندین لایه سیگنال را به گروه های ورودی/خروجی اختصاص دهید. لایههای اضافی را میتوان برای پشتیبانی از سیگنالهایی که به FPGA یا سایر رابطها (آنالوگ، SPI و غیره) اختصاص ندارند اضافه کرد.

در این استکآپ، ما بهترین گامهای موجود را برای ایجاد ایزوله در کانالهای مختلف، فراهم کردن فضای کافی و لایهها برای مسیریابی تغذیه، و ایجاد گراند فراوان برای کنترل مسیرهای برگشت برداشتهایم.

ترکیب لایه های گراند بین سیگنال و PWR بسیار مهم است زیرا کنترل مسیر بازگشت مورد نیاز ، برای اطمینان از برآورده شدن الزامات EMC را فراهم می کند. در این stackup تنها یک لایه ی تغذیه ذکر شده است، اگرچه تغذیه را نیز میتوان بر روی لایههای سیگنال مسیریابی کرد تا اتصالات با ریلهای کوچکتری برقرار شود.در سیستمهایی که جریان بیشتری وجود دارد میتوان در صورت نیاز از چندین لایه تغذیه به صورت موازی استفاده کرد.

Fanout کردن اتصال برد به برد در SOM

FPGA معمولاً دور از لبههای برد قرار میگیرد بنابراین کانالهای مسیریابی را می توان به سمت بیرون توسعه داد. با این حال، یک روش جایگزین برای قرار دادن FPGA وجود دارد. به جای قرار دادن FPGA به عنوان یک کامپوننت، ممکن است در یک سیستم روی ماژول (SOM) از طرف تامین کننده یا از یک شرکت شخص ثالث در دسترس باشد.

قرار دادن به عنوان یک SOM مستلزم fanout کردن کانکتورهای برد به برد است که می توانند تعداد پین های بسیار بالایی داشته باشند. در زیر یک مثال نشان داده شده است:

بسته به فوت پرینت کانکتور برد به برد، ممکن است به برخی از استراتژی fanout و قوانین طراحی نیاز داشته باشید که ممکن هست در یک FPGA استفاده کنید. دیدن چندین کانکتور که در یک آرایش مربع در اطراف برد SOM یا در لبه ها قرار گرفته اند، عادی است.

برنامه ریزی برای مسیریابی

با توجه به تمام بحثهای بالا، طراحی برد مدار چاپی FPGA و مسیریابی موثر با آن، کاملاً مربوط به BGA هاست، بنابراین استراتژیهای مسیریابی استفاده شده در BGA های دیگر در FPGA ها نیز قابل استفاده هستند. برای مسیریابی سیگنالها از یک FPGA بزرگ، چند استراتژی ساده لازم است:

- مطمئن شوید که فوت پرینت BGA ، FPGA شما صحیح است و با الزامات DFM مطابقت دارد.

- fanout مناسب برای BGA خود را انتخاب کنید تا سیگنال ها بتوانند به پین ها برسند

- کانال هایی را روی هر لایه ایجاد کنید که در آن رابط های خاص مسیریابی می شوند

- وسایل جانبی را در اطراف ورودی/خروجی ها بچینید تا از مسیریابی رفت و برگشت در اطراف برد جلوگیری کنند.

- از rules درطراحی خود برای اطمینان از کنترل امپدانس استفاده کنید

- differential pair geometry خود را طوری تنظیم کنید که امپدانس تحت نظر،به فاصله ی trace به گراند باشد، نه فاصله trace به trace.

سایر چالشهای جاگذاری قطعات معمولاً شامل قرار دادن خازنها بر روی پایههای تغذیه در اطراف FPGA برای decoupling است.

با بستههای BGA، این کار بسیار راحتتر است، زیرا میتوانید آن خازنها را روی پینهای پشتی FPGA قرار دهید. اگر از خازن های بزرگتر استفاده می کنید، مطمئن شوید که در مستندات ساخت خود از via-in-pad استفاده کرده اید. اگر با برخی از سریعترین استانداردهای سیگنالدهی کار می کنید، باید بسته های کوچکتری (sub-0402) را انتخاب کنید تا از سریع ترین پاسخ ممکن در شبکه decoupling خود اطمینان حاصل کنید.

برای سیگنالهای سرعت بسیار بالا، جایی که تطبیق دقیق طول در یک گذرگاه موازی بزرگ (مانند DDR4 یا بالاتر) و بین چندین differential pairs (مانند PCIe) ) مورد نیاز است.

باید flight time را در سراسر FPGA لحاظ کنید. FPGA هایی که از نظر فیزیکی بزرگ هستند ممکن است به سیگنال هایی نیاز داشته باشند که در سراسر کامپوننت حرکت کنند تا سیگنال، یک بلوک منطقی را ترک کند و به یک پایه I/O برسد. گاهی اوقات، این موارد در نقطه مقابل FPGA قرار می گیرند،بنابراین تاخیر انتشار زیادی به travel time سیگنال اضافه میشود. این flight time اضافی را می توان در اطلاعات مربوط به تاخیردر بسته های پین درFPGA گنجاند. اگر سیگنال شما در حال انتقال از طریق via است، فراموش نکنید که تاخیر via را نیز اضافه کنید.